# **ML2730** 2.4 GHZ VARIABLE DATA RATE FSK TRANSCEIVER WITH INTEGRATED PA

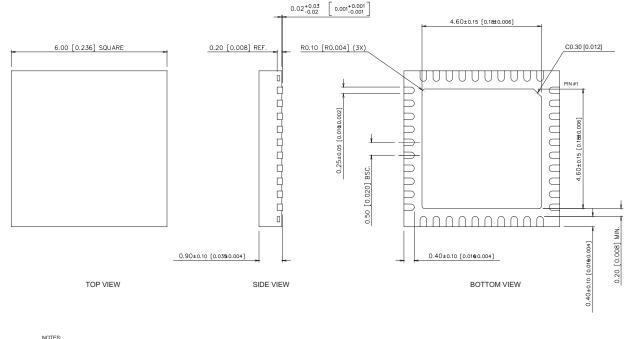

## Package: 40 QFN, 6mmx6mm

# Product Description

The ML2730 is a single chip fully integrated Frequency Shift Keyed (FSK) transceiver with fully integrated PA. It is developed for a variety of applications operating in the 2.400 GHz to 2.485 GHz unlicensed ISM band. The ML2730 is mode selectable for operation with digital cordless phones (DSSS or DECT) and higher data rate streaming applications like wireless audio and video.

The ML2730 contains a dual-conversion, low-IF receiver with all channel selectivity on chip. IF filtering, IF gain, and demodulation are performed on-chip, eliminating the need for any external IF filters or production tuning. A post detection filter and a data slicer are integrated to complete the receiver.

The ML2730 transmitter uses an adjustment-free closed loop modulator, which modulates the on-chip VCO filtered data. The ML2730 includes an upconversion mixer, a buffer/predriver, and a power amplifier to produce a typical output power of +19dBm. A fully integrated fractional synthesizer is used in both receive and transmit modes. Power supply regulation is included in the ML2730, providing circuit isolation and consistent performance over supply voltages between 2.8V and 3.6V.

| DSSS and DECT            |                                      |             |            |           |

|--------------------------|--------------------------------------|-------------|------------|-----------|

| Wireless Streaming Audio | Optimum Technology Matching® Applied | lied        |            |           |

| and Video                | 🗌 GaAs HBT                           | SiGe BiCMOS | GaAs pHEMT | GaN HEMT  |

| Wireless Data Links      | GaAs MESFET                          | Si BiCMOS   | Si CMOS    | □ RF MEMS |

|                          | InGaP HBT                            | SiGe HBT    | 🗌 Si BJT   | LDMOS     |

RF MICRO DEVICES®, RFMD®, Optimum Technology Matching®, Enabling Wireless Connectivity<sup>14</sup>, PovesStarfe, POLARIS<sup>14</sup> TOTAL RADIO<sup>14</sup> and UltimateBlum<sup>14</sup> are trademarks of RFMD, LLC, BLUETOOTH is a trade mark owned by Bulucoth SIG, Inc., U.S.A, and licensed for use by RFMD, all other trade marks, trademarks and registered trademarks are the property of their respective owners. \$2006. RF Micro Devices, Inc.

# **Features**

- +19dBm Typical Output Power From Integrated PA

- Highly Integrated 2.4GHz FSK Transceiver With Selectable Data Rates; 576kbps, 1.152Mbps, 1.536Mbps, 1.755Mbps, 2.048Mbps

- Low-IF Receiver Eliminates External IF Filters

- Fractional-N Synthesizer with 30 Hz Resolution

- Fully Integrated Digital FIR Tx Data Filter, IF Filters, FM Discriminator, and Rx Data Filter

- Self-calibrating VCO and Filters Eliminate Tuning

- Operating Modes Include DSSS-DCT, DECT, and High Rate (2.048 Mbps) for Wireless Audio and Video

- -97 dBm Sensitivity (0.1% BER) With Integrated LNA

- Includes FastWave™ Embedded Wireless Microcontroller Technology

- Simple 3-Wire Control Interface

- T/R PIN Diode or FET Switch Driver Outputs

- Analog RSSI Output: 35mV/dB

- Selectable Rx Clock Recovery Output

# **Applications**

Digital Cordless Telephones DSSS and DECT

7628 Thorndike Road, Greensboro, NC 27409-9421 · For sales or technical support, contact RFMD at (+1) 336-678-5570 or sales-support@rfmd.com.

# **ML2730**

## **Absolute Maximum Ratings**

| Parameter                                                  | Rating         | Unit |

|------------------------------------------------------------|----------------|------|

| VCC                                                        | VSS-0.3 to 3.6 | V    |

| VCC_PA                                                     | VSS-0.3 to 4.5 | V    |

| Junction Temperature                                       | 150            | °C   |

| Storage Temperature                                        | -65 to +150    | °C   |

| Lead Temperature (Soldering, 10s)                          | 260            | °C   |

| Ambient Temperature Range (T <sub>A</sub> )                | -20 to +80     | °C   |

| VCC Range [VDD (pin 9,) VCCPLL<br>(pin 19), VCCA (pin 27)] | 2.8 to 3.6     | V    |

| VCC_PA Range [VCC_PA (pin 31)]                             | 3.0 to 4.5     | V    |

| Thermal Resistance ( $\theta_{JA}$ )                       | 36             | °C/W |

→ Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EUDirective 2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

| Parameter                                                                                              | Specification |        | Unit | Condition        |                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------|---------------|--------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Farameter                                                                                              | Min.          | Тур.   | Max. | Unit             | Condition                                                                                                                                                                                                                                                                          |

| Power Supplies                                                                                         |               |        |      |                  | Unless otherwise specified $T_A = 25 \text{ °C}$ and the<br>supply voltage is $V_{CC} = 3.3 \text{ V}$ , $V_{CC\_PA} = 3.6 \text{ V}$ ,<br>$R_{ISET} = 0\Omega$ , $F_{REF} = 12.288 \text{ MHz}$ , DATA<br>RATE = 1.536 Mbps, all measurements are nor-<br>malized to the IC pins. |

| Supply current, STANDBY mode<br>(I <sub>STBY</sub> )                                                   |               | 2      |      | μА               | DC supply connected, XCEN low, RXON high.                                                                                                                                                                                                                                          |

| Supply current, STANDBY mode<br>with Patch code retention<br>(I <sub>STBY</sub> )                      |               | TBD    | 10   | μΑ               | DC supply connected, XCEN low, RXON high.                                                                                                                                                                                                                                          |

| Supply current, RECEIVE mode (I <sub>RX</sub> )                                                        |               | 63     |      | mA               | RX chain active, data being received.                                                                                                                                                                                                                                              |

| Supply current, TRANSMIT mode<br>(I <sub>TX</sub> )                                                    |               | 65     |      | mA               | TX chain active, data being transmitted.                                                                                                                                                                                                                                           |

| Supply current, TRANSMIT mode<br>(I <sub>PA</sub> )                                                    |               | 120    |      | mA               | TX chain active, data being transmitted,<br>+19dBm output.                                                                                                                                                                                                                         |

| Synthesizer                                                                                            |               |        |      |                  |                                                                                                                                                                                                                                                                                    |

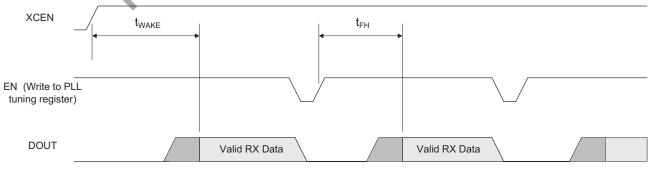

| Lock time for any in band fre-<br>quency change (RX-TX; TX-RX;<br>all combinations) (t <sub>FH</sub> ) | 0             | 50     |      | μsec             | From EN asserted to RX valid data (RX) or valid TX data to within 50 kHz of final frequency.                                                                                                                                                                                       |

| Reference signal frequency (f <sub>FREF</sub> )                                                        |               | 12.288 |      | MHz              | Data Rate = 1.5360, 1.7554, and 2.0480 Mbps                                                                                                                                                                                                                                        |

|                                                                                                        |               | 13.824 |      | MHz              | Data Rate=576, 1,152Kbps                                                                                                                                                                                                                                                           |

| Reference Signal Input Level<br>(V <sub>FREF</sub> )                                                   | 0.5           |        |      | V <sub>P-P</sub> | Clipped sine, AC coupled                                                                                                                                                                                                                                                           |

| RFMD     | •)))) |

|----------|-------|

| rfmd.com |       |

Specification Parameter Unit Condition Min. Max. Typ. Receiver 2.400 2.485 Receive input frequency range GHz (F<sub>RXI</sub>) Input Impedance Differential (Z<sub>RX</sub>) 100 Ω Differential Data Range=1.1520 Mbps Channel Spacing (F<sub>STEP</sub>) 1.728 MHz 2.048 MHz Data Range=1.5360Mbps 4.096 Data Range=1.7554 Mbps MHz 4.096 MHz Data Range=2.0480 Mbps Input Power (DR) +10 dBm <0.1%BER at 1.1520Mbps <0.1%BER at 1.5360Mbps +10 dBm +10 dBm <0.1%BER at 1.7554 Mbps +10 dBm <0.1%BER at 2.0480 Mbps Input Sensitivity (S<sub>RXI</sub>) -97 dBm <0.1%BER at 1.1520 Mbps <0.1% BER at 1.5360 Mbps -97 dBm <0.1% BER at 1.7554 Mbps -97 dBm -95 dBm <0.1% BER at 2.0480 Mbps RX conducted emissions at RXI -50 dBm RXI terminated in  $50\Omega$ (P<sub>RXI</sub>) RX Chain Image rejection ratio 23 dB (IRR) 15 RX adjacent channel(s) rejection. dB ±1 channel offset Wanted signal=-80dBm (ACR) 40 dB ±2 channels offset 45 dB ±3 or more channels offset Co-Channel rejection, 0.1% BER -9 dB Wanted signal = -80dBm, Unwanted signal is GFSK modulated with 1.536 Mbps PRBS data, (CCR) BT=0.9 RSSI RSSI rise time, 20% to 80% 5 10 μsec 20pF loading on RSSI pin RF off to -15dBm (t<sub>R\_RSS</sub>I) RSSI fall time, 80% to 20% 5 20pF loading on RSSI pin -15dBm to RF off 10 μsec (t<sub>F\_RSSI</sub>) RSSI maximum voltage (V<sub>RSMX</sub>) -10dBm into RXI 2.5 V -40dBm into RXI RSSI midrange voltage (V<sub>RSMD</sub>) 2.3 V RSSI minimum voltage (V<sub>RSMN</sub>) 0.2 V No signal applied RSSI sensitivity (V<sub>RSMXC</sub>) 35 mV/dB (V<sub>-40dBm</sub> - V<sub>-50dBm</sub>)/10dB RSSI accuracy (G<sub>RSSI</sub>) ±З dB Deviation from best fit straight line

ML2730

# **ML2730**

| RF | MD | • <b>&gt;</b> )))) |

|----|----|--------------------|

|    |    |                    |

| Specification        |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Min.                 | Тур.           | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                | Unit                                                                                                    | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2.400                |                | 2.485                                                                                                                                                                                                                                                                                                                                                                                                                               | GHz                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                      | ±400           |                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                     | Data Range=1.1520Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | ±512           |                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                     | Data Range=1.5360Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | ±596           |                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                     | Data Range=1.7554Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | ±680           |                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                     | Data Range=2.0480 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 0.5            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         | Data Range=1.1520Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | 0.9            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         | Data Range=1.5360Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | 0.8            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         | Data Range=1.7554 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 0.7            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         | Data Range=2.0480 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | -35            |                                                                                                                                                                                                                                                                                                                                                                                                                                     | dBc                                                                                                     | $P_{TXO}$ = +21 dBm, FSPUR = 1/3, 2/3, 4/3, and 5/3 $F_{TXO}$                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>DD</sub> *0.7 |                | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 0                    |                | V <sub>DD</sub> *0.3                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| -5                   |                | +5                                                                                                                                                                                                                                                                                                                                                                                                                                  | μA                                                                                                      | All states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                      | 4              | . 0                                                                                                                                                                                                                                                                                                                                                                                                                                 | pF                                                                                                      | 1MHz test frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| VDD-0.4              | ~              |                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                       | Sourcing 5.0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                      |                | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                       | Sinking 5.0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ±5.0                 | ±8.0           |                                                                                                                                                                                                                                                                                                                                                                                                                                     | mA                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| VDD-0.4              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                       | Sourcing 0.1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 0                    |                | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                       | Sinking 0.1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| VDD-0.4              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                       | Sourcing 0.1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                      |                | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                       | Sinking 0.1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                      | 1.15           |                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                      | 0.8            |                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>P-P</sub>                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                      | 2.400<br>2.400 | Min.       Typ.         2.400       1         2.400       ±400         ±512       ±596         ±596       ±680         ±680       0.5         0.9       0.8         0.7       -35         0       -35         VDD-0.7       -35         VDD-0.4       -4         ±5.0       ±8.0         VDD-0.4       -4         VDD-0.4       -4         VDD-0.4       -4         VDD-0.4       -4         VDD-0.4       -4         1.15       -4 | Min.       Typ.       Max.         2.400       2.485         2.400 $2.485$ $\pm 400$ 2.485 $\pm 512$ $$ | Min.         Typ.         Max.         Unit           2.400         2.485         GHz $\pm 400$ $kHz$ $kHz$ $\pm 512$ $kHz$ $kHz$ $\pm 596$ $kHz$ $kHz$ $\pm 596$ $kHz$ $kHz$ $\pm 680$ $kHz$ $kHz$ $0.9$ $kHz$ $kHz$ $0.7$ $dBc$ $dBc$ $0.7$ $dBc$ $dBc$ $0.7$ $VDD$ $V$ $0.7$ $VDD$ $V$ $0.7$ $VDD$ $V$ $VDD^{0}$ $V$ $V$ $VDD^{0}$ $V$ $V$ $VDD^{0}$ $V$ $V$ $VDD^{-0.4}$ $V$ |  |

| Parameter                                                       | Specification |      | Unit | Condition |           |

|-----------------------------------------------------------------|---------------|------|------|-----------|-----------|

| Farameter                                                       | Min.          | Тур. | Max. | Unit      | Condition |

| 3 Wire Serial Bus Timing                                        |               |      |      |           |           |

| CLK Input Rise Time (Note 1) (t <sub>r</sub> )                  |               |      | 15   | ns        |           |

| CLK Input Fall Time (Note 1) (t <sub>r</sub> )                  |               |      | 15   | ns        |           |

| CLK Period (t <sub>ck</sub> )                                   | 50            |      |      | ns        |           |

| EN Pulse Width (t <sub>ew</sub> )                               | 200           |      |      | ns        |           |

| Delay from last Clock Rising Edge to Rise of EN $(t_j)$         | 15            |      |      | ns        |           |

| EN Setup Time to Ignore next Ris-<br>ing CLK (t <sub>se</sub> ) | 15            |      |      | ns        |           |

| Data-to-CLK Setup Time (t <sub>s</sub> )                        | 15            |      |      | ns        |           |

| Data-to-CLK Hold Time (t <sub>h</sub> )                         | 15            |      |      | ns        |           |

Note 1: Serial I/O clock maximum rise and fall times are based on the minimum clock period. Longer rise and fall times can be accommodated for slower clocks provided the rise and fall times remain less than 20% of the clock period and all set up and hold time minimums are met with respect to the CMOS switching points (V<sub>IL</sub> MAX and V<sub>IH</sub> MIN). The serial I/O clock rise and fall times are limited to an absolute maximum of 100 ns.

**ML2730**

| Pin | Function  | Description                                                                                                                                                                                                                          | Interface Schematic                                                                                            |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1   | XCEN      | Transceiver Enable input. Enables the bandgap reference and voltage regulators when high, enabling normal control functions. Consumes only leakage current in STANDBY mode when low. Operating mode= $V_{IH}$ Standby mode= $V_{IL}$ | VDD         VDD         VDD           160 0hm         VDD         VDD           VSSD         VSSD         VSSD |

| 2   | RXON      | TX/RX Control Input. Switches the transceiver between TRANSMIT and<br>RECIEVE mode.<br>Receive mode=V <sub>IH</sub><br>Transmit mode=V <sub>IL</sub>                                                                                 | RXON 260 Ohm<br>Vac Vac Vac<br>Z60 Ohm<br>VSSD VSSD VSSD                                                       |

| 3   | SW_CTRL_P | TR switch control output, positive polarity.<br>Logic high (V <sub>OL</sub> ) while transmitting<br>Logic low (V <sub>OL</sub> ) while receiving                                                                                     | Voo Voo<br>150 ohm<br>SW_CTRL_F<br>VSSD VSSD VSSD                                                              |

| 4   | DIN       | Transmit Data Input.                                                                                                                                                                                                                 | UN 160 Ohm                                                                                                     |

| 5   | VSSD      | Digital ground for all digital I/O circuits and control logic.                                                                                                                                                                       |                                                                                                                |

| 6   | EN        | Control Bus Enable. Enable pin for the three-wire serial control bus. The control registers are loaded on the rising edge of this signal. Serial control bus data is ignored when this signal is high ( $V_{IH}$ ).                  | EN LISO ohm<br>VSSD VSSD VSSD                                                                                  |

| 7   | DATA      | Serial Control Bus Data.                                                                                                                                                                                                             | DATA                                                                                                           |

| Pin      | Function     | Description                                                                                                                                 | Interface Schematic                                                |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 8        | CLK          | Serial control bus data is clocked in on the rising edge and only when EN is low.                                                           |                                                                    |

|          |              |                                                                                                                                             |                                                                    |

| 9        | VDD          | 3.3V <sub>DC</sub> power supply input.                                                                                                      |                                                                    |

| 10       | VREG_1P8     | 1.8V <sub>DC</sub> regulator output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator. |                                                                    |

| 11       | VBG_1P8      | $1.13V_{DC}$ bandgap voltage output. Place capacitor between this pin and ground to decouple (bypass) noise.                                |                                                                    |

| 12       | FREF         | Input reference frequency.                                                                                                                  | FREF KSSD                                                          |

| 13<br>14 | VCCSYN       | 2.7V <sub>DC</sub> power supply input. Must be connected to VREGPLL pin externally.<br>Loop filter control switch.                          |                                                                    |

|          | PLL_SW       | Ren                                                                                                                                         | PLLSW<br>DOWNBOND                                                  |

| 15       | QPO<br>VTUNE | Charge pump output of the phase detector. This is connected to the exter-<br>nal PLL loop filter.                                           | VCCSYN<br>20 Ohm QPO<br>20 Ohm QPO<br>DOWNBOND<br>VREGVCO<br>VTUNE |

| 17       | VREGVCO      | 2.5V <sub>DC</sub> regulator output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator. |                                                                    |

| 18       | VREGPLL      | $2.7V_{DC}$ power supply output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator.     |                                                                    |

| 19       | VCCPLL       | $3.3V_{DC}$ power supply input. Place capacitor between this pin and ground to decouple (bypass) noise.                                     |                                                                    |

| 20       | VBG_VCO      | $1.13V_{DC}$ bandgap voltage output. Place capacitor between this pin and ground to decouple (bypass) noise.                                |                                                                    |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                    | Interface Schematic    |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 21  | VREGLNA  | $2.7V_{DC}$ regular output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator.                                                                                                                                                                             |                        |

| 22  | RXIN     | Differential receive RF Input.                                                                                                                                                                                                                                                                                 |                        |

| 23  | RXIP     | Differential receive RF Input.                                                                                                                                                                                                                                                                                 |                        |

| 24  | VREGRX   | 2.7 V <sub>DC</sub> regular output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator.                                                                                                                                                                     | <u>.</u>               |

| 25  | VBG_RF   | Bandgap 1.24V decouple voltage. Decoupled to ground with a capacitor.                                                                                                                                                                                                                                          |                        |

| 26  | VREGTX   | $2.7V_{DC}$ power supply input. Must be connected to VREGRX pin externally.                                                                                                                                                                                                                                    | $\mathbf{\mathcal{S}}$ |

| 27  | VCCA     | 3.3V <sub>DC</sub> power supply input.                                                                                                                                                                                                                                                                         |                        |

| 28  | ТХО      | TX RF open-collector output. Connect this pin to VCC using an (RF blocking) inductor.                                                                                                                                                                                                                          | DOWNBOND               |

| 29  | ISET     | TX I <sub>SET</sub> resistor.                                                                                                                                                                                                                                                                                  |                        |

| 30  | VBG_PA   | $1.13V_{DC}$ bandgap voltage output. Place capacitor between this pin and ground to decouple (bypass) noise.                                                                                                                                                                                                   |                        |

| 31  | VCC_PA   | Unregulated Battery DC Power Supply Input.                                                                                                                                                                                                                                                                     |                        |

| 32  | VREGPA   | $\label{eq:programmable} \begin{array}{l} \mbox{Programmable 3.67V}_{DC} */3.44V_{DC} / 3.3V_{DC} \mbox{ regulator output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator. \\ *Not recommended for use - Exceeds Absolute Maximum Ratings. \end{array}$ |                        |

| 33  | VREGIF   | 2.7 V <sub>DC</sub> regular output. Place capacitor between this pin and ground to decouple (bypass) noise and to stabilize the regulator.                                                                                                                                                                     |                        |

| 34  | TPI      | RX/TX test port. Used to test or apply test signals to both RX and TX sec-<br>tions.                                                                                                                                                                                                                           |                        |

| 35  | TPQ      | RX/TX test port. Used to test or apply test signals to both RX and TX sec-<br>tions.                                                                                                                                                                                                                           |                        |

| ML: | 2730 |

|-----|------|

|-----|------|

| Pin | Function                      | Description                                                                                                                                                                                                                                                                                                                                       | Interface Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36  | RSSI                          | Receive Signal Strength Indicator. Also used as RX/TX test port.                                                                                                                                                                                                                                                                                  | OPAMP<br>MUX<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 37  | AOUT                          | Analog data output.                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 38  | DOUT                          | Serial digital output after demodulation, bit rate filtering and center data slicing. CMOS levels with controlled slew rates.                                                                                                                                                                                                                     | CEH (nigh drive output enable) VDD VDD VDD DDD VDD VDD VDD VDD VDD VD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 39  | DATASEL<br>or<br>PLL_Lock     | When TCMOD=4 or 5, this pin becomes an input and it controls the time constant of the data slicer.<br>DATASEL= $V_{IH}$ selects 6 uS time constant<br>DATASEL= $V_{IL}$ selects 300 uS time constant<br>-else-<br>PLL_Lock= $V_{DH}$ indicates PLL is locked<br>PLL_Lock= $V_{DL}$ indicated PLL is not locked                                    | DATASEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 40  | SW_CNTRL<br>_N<br>or<br>RXCLK | TR switch control output, negative polarity.<br>$V_{OL}$ while transmitting<br>$V_{OH}$ while receiving<br>-or-<br>Recovered RXCLK clock output is multiplexed in this pin. When configured<br>for RXCLK output, clock pulses may be observed for 6 uS to 8 uS after the<br>falling edge of RXON before setting to logic high (V <sub>IH</sub> ). | OF<br>(bigh drive adject erable)<br>(high drive adject erable) |

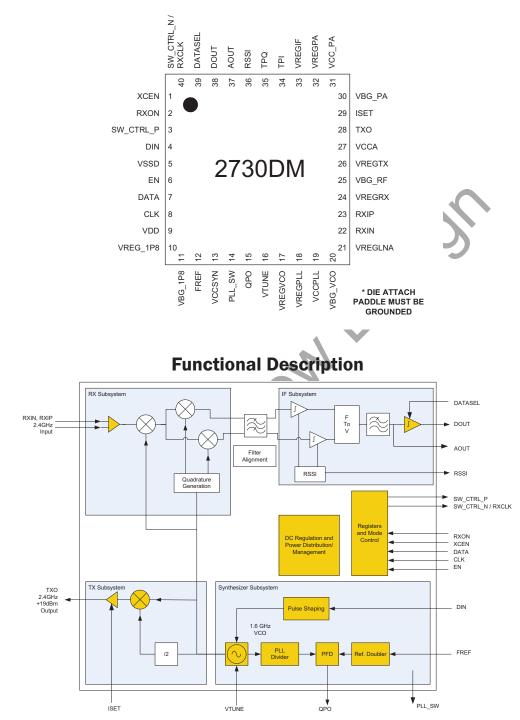

# **Pin Configuration (Top View)**

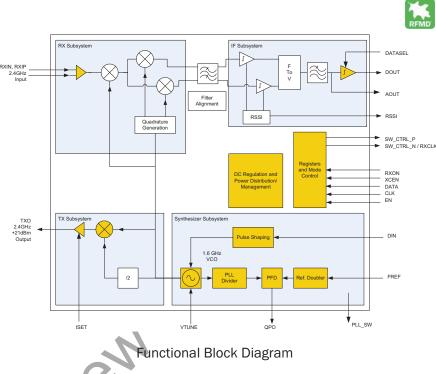

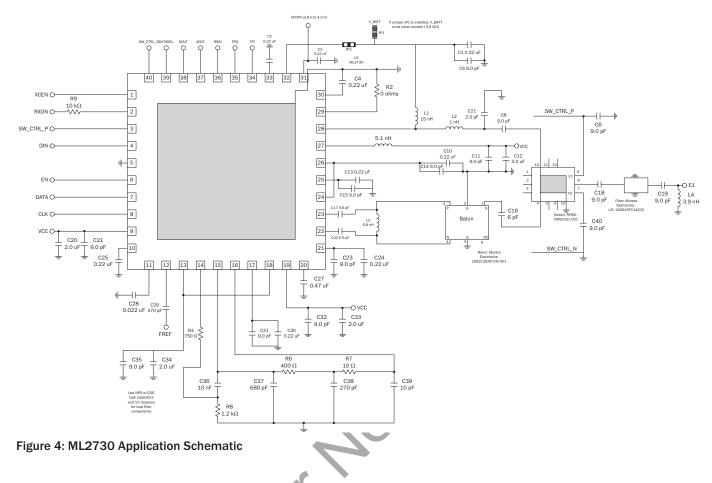

Figure 1: ML2730 Block Diagram

The ML2730 is a single chip wireless digital transceiver. The ML2730 integrates all the frequency generation, receiver and transmit functions requiring only a TR switch to form a complete 2.400GHz to 2.485GHz ISM radio band. The ML2730 is designed to transmit and receive 576kbps to 2.048Mbps signals using channels spaced from 1.728MHz to 4.096MHz over the 2.400GHz to 2.485GHz ISM band.

#### Receiver

The ML2730 contains a dual conversion, low\_IF receiver with all channel selectivity on-chip. The signal enters through a differential LNA to the 1st mixer which down-converts the 2.4GHz input to a high 1st IF of 0.8GHz, followed by an image reject 2nd mixer that brings this IF signal down to a low IF frequency. On chip IF filtering, gain, and demodulation are performed at a 864kHz IF frequency for the 576kbps and 1.152Mbps data rate, a 1.024MHz IF frequency for the 1.536Mbps data rate, or a 2.048MHz IF frequency for the 1.755Mbps and 2.048Mbps data rates.